的使用是不可避免的。在标准的电路板上,元器件被放置在顶层,而差分对的走线在内层。内层的电磁辐射和对与对之间的串扰较低。必须使用

幸运的是,可设计出一种透明的过孔来最大限度地减少对性能的影响。在这篇博客中,我将讨论以下内容:

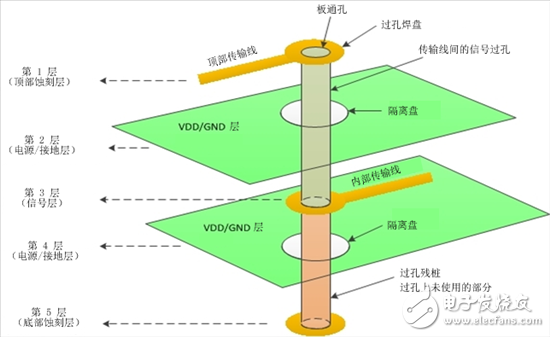

让我们从检查简单过孔中将顶部传输线与内层相连的元件开始。图1是显示过孔结构的3D图。有四个基本元件:信号过孔、过孔残桩、过孔焊盘和隔离盘。

过孔是镀在电路板顶层与底层之间的通孔外的金属圆柱体。信号过孔连接不同层上的传输线。过孔残桩是过孔上未使用的部分。过孔焊盘是圆环状垫片,它们将过孔连接至顶部或内部传输线。隔离盘是每个电源或接地层内的环形空隙,以防止到电源和接地层的短路。

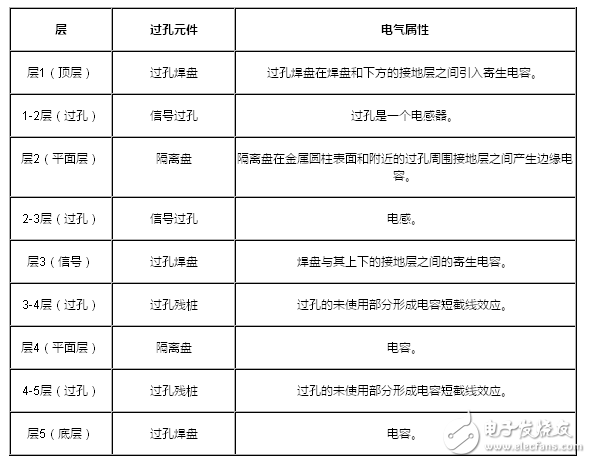

一个简单过孔是一系列的型网络,它由两个相邻层内构成的电容-电感-电容 (C-L-C) 元件组成。表格2显示的是过孔尺寸的影响。

通过平衡电感与寄生电容的大小,可以设计出与传输线具有相同特性阻抗的过孔,从而变得不会对电路板运行产生特别的影响。还没有简单的公式能在过孔尺寸与C和L元件之间进行转换。3D电磁 (EM) 场解算程序能根据PCB布局布线中使用的尺寸来预测结构阻抗。通过重复调整结构尺寸和运行3D仿真,可优化过孔尺寸,来实现所需阻抗和带宽要求。

我们曾在之前的帖子中讨论过,在实现差分对时,线路A与线路B之间必须高度对称。这些对在同一层内走线,若需要一个过孔,必须在两条线路的临近位置上打孔。由于差分对的两个过孔距离很近,两个过孔共用的一个椭圆形隔离盘能够减少寄生电容,而不是使用两个单独的隔离盘。接地过孔也被放置在每个过孔的旁边,这样的话,它们就能够为A和B过孔提供接地返回路径。

图2显示的是一个地-信号-信号-地 (GSSG) 差分过孔结构示例。两个相邻过孔间的距离被称为过孔间距。过孔间距越小,互耦合电容越多。

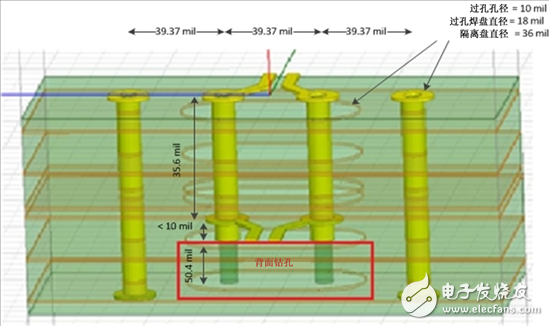

不要忘记,在传输速率超过10Gbps时,过孔残桩会极度影响高速信号完整性。幸运的是,有一种背面钻孔PCB制造工艺,此工艺可以在未使用的过孔圆柱上钻孔。根据制造工艺公差的不同,背面钻孔去除了未使用的过孔金属,并最大限度地将过孔残桩减少到10mil以下。

3D EM仿真器用来根据所需的阻抗和带宽来设计差分过孔。这是一个反复的过程。此过程重复地调整过孔尺寸,并运行EM仿真,直到实现所需的阻抗和带宽。

图2中显示的差分过孔设计已构建完毕并经测试。测试样片包括顶层的一对差分线,之后是到内部差分线的差分过孔,然后第二对差分过孔再次连接至顶层的球状引脚栅格阵列封装 (BGA) 接地焊盘。信号路径的总长度大约为1330mil。我用差分时域反射仪 (TDR) 测得其差分阻抗,用网络分析仪测得了带宽,并用高速示波器测量了数据眼图来了解其对信号的影响。图3,4,5分别显示了阻抗、带宽和眼图。左图是使用背面钻孔时的测试结果,而右图是无背面钻孔的测试结果。在图5中的带宽波特图中,我们大家可以很清楚地看到背面钻孔对于在数据速率大于10Gbps 的情况下实现高性能是必不可少的。

使用背面钻孔,ZDIFF大约为85? 无背面钻孔,ZDIFF大约为58?

TI拥有丰富的高速信号调理集成电路 (IC)产品库,诸如retimer和redriver。它们有助于减轻和缓解所有类型差分对的缺陷和高插入损耗,以此来实现先进系统中的可靠数据通信并扩展传输距离。

请在下面进行留言我很想听一听你对这篇帖子的反馈,或者是你希望从以后的“差分对”帖子中了解哪些内容。

仔细阅读TI两端口40千兆以太网 (40GbE)/10GbE四通道小外观尺寸可插拔 (QSFP+) 信号调节器参考设计。

阅读与WEBENCH® 接口设计人员工具相关的更多内容。这一工具能够在一定程度上帮助设计人员使用TI信号调理IC来解决差分对损坏问题。

产品系列

Products

联系我们

乐鱼app下载电话

乐鱼app下载: 乐鱼官网_官方app下载

邮编: 518126

联系人: 王经理

热线: 400-800-7156

电话: 0755-26414638

传真: 0755-26522816

邮箱: szcreate@163.com

QQ: 631045164

![[field:text/]](/ms/static/picture/2-1f4211u004.jpg)

![[field:text/]](/ms/static/picture/2-1f4211u004-50.jpg)

![[field:text/]](/ms/static/picture/2-1f424161600.jpg)

首页

首页

产品

产品

案例

案例

联系

联系