本发明的公开宽泛地涉及信息处理系统的领域,更具体而言涉及场微 电子封装技术。

芯片的高密度互连或空间转换以便能够将IC (集成电路)安装到印刷电路板上。芯片封装的系统性能和成本需求驱使着设计者使用低成^r机芯片 载体代替更昂贵的陶瓷或玻璃材料.然而,有机芯片栽体与硅集成电路芯片之间的热膨胀系数(CTE)失配是一个挑战。在工作期间由环境和温度漂 移和引起芯片封装结构中气温变化的由芯片产生的热所引起的热膨胀系数 失配造成了组件之间的机械应力.

使用有机芯片载体的解决方案包括在芯片和第一级封装之间的环氧树 脂底部填充以减少在可控塌陷芯片连接(C4)互连上的表面应变。此外, 早先已经提出了解决方案以构建柔性(compliant)互连.因此,需要制造 低成本柔性互连。

此外,已经提出;OL极高密度珪芯片栽体作为IC和下级封装之间的 中间插入物以提供极高互连密度和对于硅芯片的CTE匹配.这将减少在 硅芯片与CTE匹配的珪芯片栽体之间的C4焊料互连上的热引起的应力, 并能减小C4的尺寸和增加的I/O密度,然而,在下级封装是有机基板的 情况下,硅芯片载体的CTE将不会匹配到有机基板,这将导致在载体与 下层封装之间的C4焊料互连上的应力。因此,存在提供在硅芯片栽体与 下层封装之间的柔性的需要。 发明内容根据本发明的实施例,通过提供柔性的通孔结构实现一种用于向由硅或另一 CTE匹配的材料制造的芯片栽体并入柔性的方法和系统.在本发明的另 一实施例中,通过将柔性结构并入到芯片基H自身中实 现在所述芯片与所述下级封装之间的柔性。

图l是根据本发明的实施例的硅插入物的图;图2示出了根据本发明的实施例的柔性互连;图3A-L示出了用柔性材料制造通孔的方法;图4A-0示出了用空隙制造通孔以形成柔性的方法;图5A-C示出了在硅芯片中制造的集成柔性;图6示出了安装在有机M上的芯片;图7示出了沿纵和垂直方向都揭 供柔性的柔性互连;以及图8示出了其它更复杂的几何形状例如S形柱和L形柱。

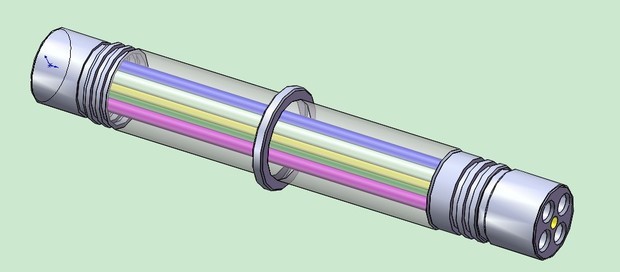

高密度芯片载体的^Ol包括与芯片CTE匹配的材料例如硅或陶瓷以 提供较高互连密度和带宽。如图1所示,硅芯片载体104提供与硅芯片102 CTE匹配的^。这将减少在珪芯片与CTE匹配的硅芯片载体之间的C4 微连接焊料互连上的热引起的应力,并能减小C4的尺寸和增加的I/O密 度。硅芯片栽体使用通孔和C4焊料互连为功率、地和信号提供到达下级 封装的通路。在下级封装是有机J41的情况下,硅芯片载体的CTE将不 会匹配到有机基板,这将导致C4焊料互连上的应力。因此,存在提供在 硅芯片栽体与下层封装之间的柔性的需要。参考图1,示出了根据本发明的实施例的芯片封装100的图。芯片封 装包括两个电子芯片102,其顶侧通过焊料凸起连接到芯片的底侧的硅栽

体104。载体104还包括与芯片102的CTE近似匹配的CTE,根据本发 明的实施例,载体104包括从载体的底侧到载体的顶侧的多个柔性通孔 107。参考图2,示出了通孔107的结构。每个通孔结构107包括在载体204 的顶表面处暴露的导电(优选铜)通孔环垫(collar) 202。在栽体204的 底表面暴露优选铜衬垫212,和在环垫202与衬垫212之间设置优选铜通 孔柱206,CTE匹配的芯片载体204由其中通孑L提供柔性和通路以同时增加I/O 密度和对有机基H 216的互连柔性的材料例如珪制造。例如,硅的CTE 约3卯m (百万分之)和有机基板处于13-15卯m之间。对于50C的温度 变化40 mm平方的载体产生的CTE失配将导致栽体与有机ljfeL之间的约 IO微米的横向位移。导电铜结构延伸通过硅栽体基板204中的孔208。用低模量材料填充 孑L将铜环垫202接合到硅芯片栽体204的顶表面并将其附装到铜柱206, 又将所述铜柱206附装到支撑铜衬垫/BLM (球限冶金)212的铜微衬垫。 例如,这样产生C4焊料微连接210:在铜衬垫/BLM (球限冶金)212上 m鉛锡焊料球,然后熔化铅锡焊料球以将212连接到在下级封装结构上 的匹配焊料^衬垫/TSM (顶表面冶金)214,其中所迷下级封装结构在 该情况下是有机基板216。因为通过孔的铜柱206自由浮动在硅芯片载体204中或者由柔性材料 软支撑,因此相对有机基板216的珪芯片载体204的热膨胀将导致沿纵向 的铜柱206的挠曲。该柔性将减小在C4焊料微连接210上的热机械引起 的应力,该C4焊料微连接210连接铜衬垫/BLM 212与焊料衬垫/TSM 214 以制造硅载体204与下级封装有机基长216之间的电连接。图7中示出了提供沿垂直和纵向具有柔性的通孔结构的方法,在该实 施例中,以相对于垂直安装方向的角度^ 718制造铜柱708.例如,角度 可以处于30至45度之间,响应垂直力,柱将弯曲以提供沿垂直方向的柔 性同时提供沿纵向的柔性.虽然对于倾斜柱的实施例示出了实例,但也可

提供沿所有方向的柔性。具有软材料的柔性通孔在图3A-L中示出了根据本发明的另一实施例的一种使用软材料制造 柔性通孔的方法。在步骤302中用光致抗蚀剂构图硅。在步骤304中使用 公知的深RIE (反应离子蚀刻)方法在硅晶片中蚀刻环孔(aimulus)。在 蚀刻后,如步骤306中所示使用热生长的氧化物隔离通孔。在步骤308中 用柔性材料填充环孔,例如该柔性材料可以为具有比硅的模量低得多的模 量的光致抗蚀剂或环氧树脂.在步骤310中再次构图硅,随后是去除氧化 物的RIE和去除珪中心柱的DRIE (深反应离子蚀刻)。在步骤314中再 次构图硅,和在步骤316中4tlt铜以形成通孔环垫和柱。在步骤318中研 磨并抛光晶片的背侧以暴露铜柱。在步骤320中构图晶片的背侧,和在步 骤322中镀敷形成铜衬垫和BLM。在步骤324中使用镀敷或者其它转移 方法将C4焊料突起制造到BLM上。具有间隙的柔性通孔在图4中示出了根据本发明的另一实施例的一种在间隙中制造通孔的 方法,在步骤402中使用光致抗蚀剂构图硅基板和在步骤404中用深M 离子蚀刻环状通孔,在步骤406中在每个环状通孔的表面和侧壁上生长热 氧化物,和在步骤408中用多晶硅填充每个环状通孔。在步骤410中平面 化WL,和在步骤412中生长氧化物。在步骤414中用光致抗烛剂构图顶 表面,和在步骤416中蚀刻氧化物和硅至超过多晶珪环状通孔的深度.在 步骤418中构图顶表面并用铜4tlt顶表面以形成通孔环垫和柱。在步骤420 中研磨、抛光并蚀刻晶片的背侧以暴露铜通孔柱.在步骤422中构图晶片 的背侧,和在步骤424中皿铜衬垫和BLM。在步骤426中构图晶片的 背侧以暴露围绕铜通孔的珪.在步骤428中选择性地例如用二氟化氙蚀刻 围绕铜柱的硅。在通孔壁上的氧化硅提供蚀刻停止并且二氟化氙去除围绕铜柱的硅以 限定间隙,在步骤430中使用镀敷或者其它转移方法将焊料突起制造到

BLM结构上,导致在^板内自由浮动的通孔柱。这允许通孔柱的柔性。 总之,能够正常的使用结合提供柔性的集成通孔技术的与硅CTE匹配的硅芯片栽体,以提供用于系统集成的高密度i/o和增加的柔性的技术方案。尽管上述描述针对珪芯片栽体,但是能使用接近匹配硅的CTE并允许 加工通孔的任何材料。如图l和2所示,使用硅插入物(或载体)的另一选择为直接将柔性 互连并入到硅芯片中.如图5A所示,硅器件包括这样的硅基仗500,其包 括有源器件层502和几个BEOL (后段制程)金属互连层504,所述金属 互连层504包括C4衬垫506,所述C4衬垫506承载将芯片附装到下级封 装的焊料凸起508。如图6中所示,将芯片602直接附装到有机栽体a 606。在该情况下,通过C4焊料微连接604的柔性确定在芯片602与下级 封装606之间的柔性。在BEOL布线结构上产生的热M应力将依赖相对 于载体的芯片的CTE失配、相对于栽体的芯片的温度A和微连接的柔性。如图5B中所示,可以将柔性互连结构510集成到在!^41 516上制 造的具有有源器件512的硅芯片中,该^板516包括通孔518、 520以将 BEOL布线。在该情况下,通过与C4微连接的柔 性串联的通孔柔性确定位于芯片与下级封装之间的柔性,通孔铜环垫514 附装到^141516而不是8£01^布线。结果,归因于相对于基板的芯 片的CTE失配的热;^应力没有被直接施加到BEOL布线B中的通孔柔性以满足封装的需要.在需要通孔柔性的情况 下,这能够最终靠在520所示出的间隙或低模量材料内的铜柱实现.在热机 械应力处于C4微连接与硅栽体基板的可接受的应力范围的情况下,通孔 的柔性需要近乎为零,这能够最终靠并入518中所示出的用铜完全填充而没 有间隙或低柔性材料的通孔实现。图5B的附加的设计有益效果为消除了^141500至图6中示出的热 沉608的热阻抗。图5C中示出的笫二制造选择使用例如绝缘体上珪技术将有源器

件532设置在BEOL布线的顶上。在该情况下,通孔不通过有源器件 区域从而提供用于电路制造的更多的硅区域。通孔环垫536附装到^J4! 530以减少热M应力在BEOL上的效果。如图5B中所示,依赖柔性需 要,通孔可具有间隙或者低模量材料538或者为完全填充540,也可以 通过将有源层532设置在芯片结构的最顶表面处消除图5A中示出的a 板500和图5B中示出的BEOL布线的热阻抗,由此产生更有效的热 通路。因此,虽然已经描述了目前认为是优选的实施例,但本领域的技术人 员将理解在本发明的精神内能做出其它的修改。

1. 一种电子器件,包括至少一个电子芯片,其包括顶侧、底侧、和笫一热线胀系数;以及 载体,其包括底侧和顶侧,所述顶侧连接到所述芯片的所述底侧,所 述载体还包括近似匹配所述第一热线胀系数的第二热线胀系数,和从所述 栽体的所述底侧至所述载体层的所述顶侧的多个通孔,每个通孔包括在所 述栽体的顶表面处暴露的环垫,在所述载体的底表面处暴露的衬垫,和在 所述环垫与所述衬垫之间设置的柱,其中所述柱延伸通过一定体积的空的 空间。

2. 根据权利要求l的器件,其中用^f&漠量材料填充所述体积的空的空间。

3. 根据权利要求l的器件,还包括_^良,所述基板包括不匹配所述第 一热线胀系数的第三热线胀系数,和其中通过焊料凸起将所ii^连接到 所述载体的底侧.

5. 根据权利要求l的器件,其中所述柱以不垂直于所述载体基板的角 度制造。

6. 根据权利要求l的器件,其中所述柱包括曲线的器件,其中所述基板由有机材料构成。

8. —种在硅载体中制造柔性通孔的方法,所描述的方法包括以下步骤 构图所述硅栽体;使用深反应离子蚀刻方法在所述硅栽体中蚀刻环孔; 使用热生长氧化物以隔离所述通孔; 用柔性材料填充所述环孔; 构图所述珪;进行反应离子蚀刻以去除所述氧化物和深反应离子蚀刻以去除硅中心柱;再次构图所述珪以在所述珪中形成通孔; 铜镀敷所述硅以形成通孔环垫和柱; 研磨所述载体的背侧以暴露铜柱;构图所述载体的背侧和l^lt所述载体以形成铜衬垫和球限冶金;以及 使用镀敷或其它转移方法在所述球限冶金上形成焊料凸起。

11. 一种在栽体中制造通孔的方法,包括以下步骤通过深反应离子蚀刻在所述141中蚀刻环状通孔;在所述M上生长热氧化物;用多晶硅填充所述环状通孔;平面化和氧化所iU4l;用光致抗蚀剂构图所ili4l的顶表面;蚀刻所述基板的氧化物和硅至超过所述多晶硅环状通孔的深度;构图所述顶表面并用铜4^lt以形成通孔环垫和柱;减薄所述晶片的背侧以暴露铜通孔柱;构图所述晶片的背侧;镀敷所述铜衬垫和球限冶金;构图所述晶片的背侧以暴露围绕所述铜通孔的硅;以及 用二氟化氣蚀刻围绕所述铜柱的硅。

12. —种硅芯片,包括珪M,包括有源器件层,和连接到所述有源器件的后段制程布线, 多个衬垫,以及将所^段制程布线连接到衬垫的多个通孔。

14. 依据权利要求12的硅芯片,其中所述通孔延伸通过一定体积的空 的空间或低模量材料。

15. 依据权利要求12的硅芯片,其中所述通孔包括以不垂直于所述硅基板的角度制造的柱。

16. —种包括顶部和底部的硅芯片,所述珪芯片包括硅m,包括在所述硅芯片的所述顶部处的有源器件层,和在所述有 源器件下连接的后段制程布线,在所述硅芯片的所述底部上的多个衬垫, 以及将所述后段制程布线连接到衬垫的多个通孔。

17. 根据权利要求16的硅芯片,其中使用绝缘体上硅技术在所述有源 器件下连接所述后段制程布线。

全文摘要一种电子器件包括包括第一热线胀系数(CTE)的至少一个电子芯片,和通过焊料凸起将芯片的顶侧连接到底侧的载体。所述载体还包括近似匹配所述第一CTE的第二CTE,和从载体的底侧至载体层的顶侧的多个通孔。每个通孔包括在载体的顶表面处暴露的环垫、在载体的底表面处暴露的衬垫、以及在环垫与衬垫之间设置的柱。所述柱延伸通过一定体积的空间。

工程电磁场与磁技术,无线.气动光学成像用于精确制导 2.人工智能方法用于数据处理、预测 3.故障诊断和健康管理

电子器件用基板及其制造方法、使用该基板的电子器件及其制造方法和有机led元件用基板的制作方法

一种允许电子器件和电池之间通信的方法、一种包括电子器件和电池的装置和一种允许 ...的制作方法

铁掺杂的二硒化镍微米花作为可充室温镁电池正极活性材料的应用的制造方法与工艺

产品系列

Products

联系我们

乐鱼app下载电话

乐鱼app下载: 乐鱼官网_官方app下载

邮编: 518126

联系人: 王经理

热线: 400-800-7156

电话: 0755-26414638

传真: 0755-26522816

邮箱: szcreate@163.com

QQ: 631045164

![[field:text/]](/ms/static/picture/2-1f4211u004.jpg)

![[field:text/]](/ms/static/picture/2-1f4211u004-50.jpg)

![[field:text/]](/ms/static/picture/2-1f424161600.jpg)

首页

首页

产品

产品

案例

案例

联系

联系